Protel_DXP编译项目及生成原理图报表

发布时间:2017-06-15 点击次数:次

【目标】

学习编译项目,产生ERC报告,会纠正报告中的错误;会生成原理图的网络表、元器件列表。

【范例】

以图2-1所示的555定时器组成的振荡器电路原理图为例,生成该原理图的ERC表、网络表、元器件列表。

【步骤】

打开或新建一个工程文件Myproject1. PrjPCB,把振荡器电路原理图放入该工程下。

(1)产生ERC报告

ERC即电气规则检查。主要用于在进行PCB设计之前,对电路原理图中电路连接匹配的正确性进行检验。执行完该检查后,系统将自动在原理图中有错的地方加以标记,从而方便用户检查错误,提高设计质量和效率。

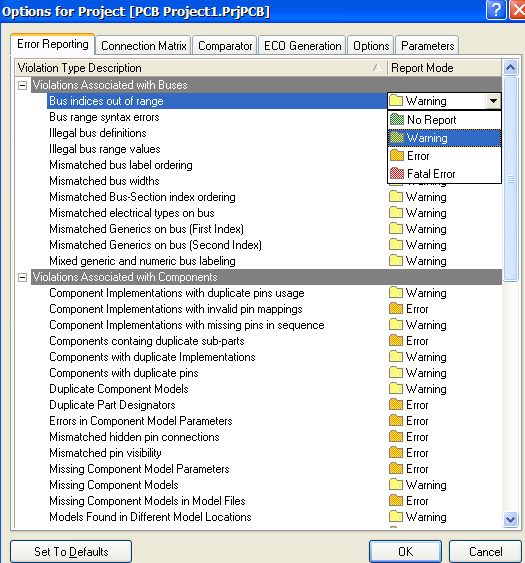

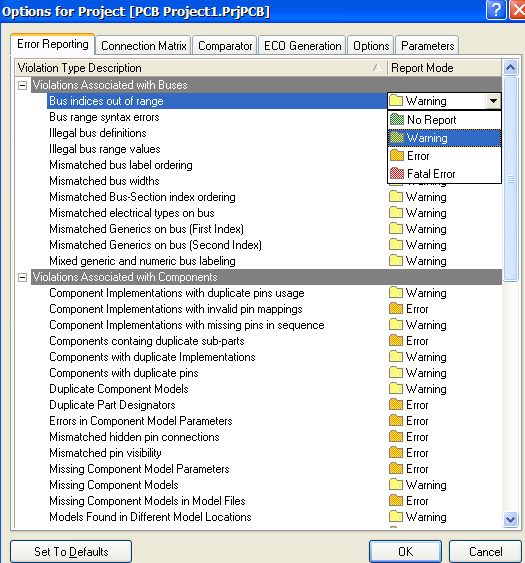

① 在对所绘原理图进行ERC检测之前应对ERC规则进行设置。ERC规则进行设置在“Options for Project”对话框实现,执行Project→Project Options命令,将弹出如图4-1所示的对话框。其中涉及到电路原理图检查的有Error Reporting(错误报告)和Connection Matrix(连接矩阵)两个。一般采用默认设置不需要对错误报告类型进行修改。

图4-1 项目管理选项对话框

② 编译项目 (ERC检查)

编译项目就是在设计文档中检查原理图的电气规则错误。执行菜单命令 Project / Compile PCB Project ,系统开始编译 Myproject1. PrjPCB 。当项目被编译时,在项目选项中设置的错误检查都会被启动,同时弹出 Message 窗口显示错误信息。如果原理图绘制正确,将不会弹出 Message 窗口。

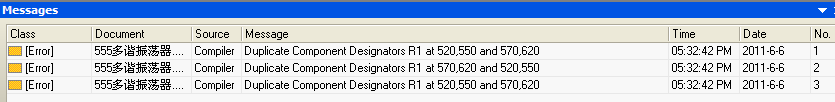

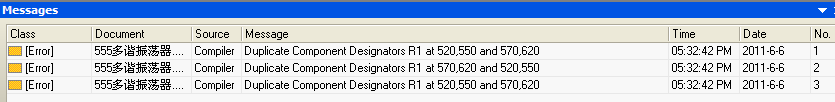

故意把电阻R重名,编译后弹出如图4-2所示信息。

图4-2 ERC错误报告

双击一个出错信息前面的颜色方块,则会弹出与此错误有关的原理图信息,显示在Compile Error 对话框。如图4-3所示。

图4-3 Compile Error 对话框

从 Compile Error 对话框中单击错误跳转到原理图的违反对象进行检查或修改。此时修改对象高亮显示,电路图上的其他元件和导线模糊。修改完成后,可以单击图纸有下方的 Clear 按钮,清除图纸的模糊状态。

修改完成后,重新编译项目,直至不再显示错误为止。保存项目文件。

(2)生成网络表

网络表文件是简单的ASCII码文本文件,共包含两部分:元器件描述和元器件的网络连接描述。

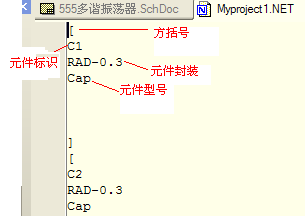

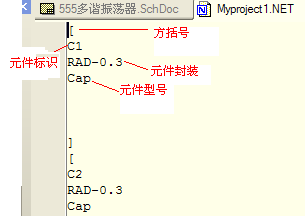

执行主菜单命令 Design/Netlist/Protel,产生与原项目文件同名,后缀名为.net的网络表,这里生成的网络表名称即为Myproject1. net,如图4-4所示。

双击Myproject1. net 图标,将显示网表的详细内容。如图4-5所示。

图4-4 网络表的生成

图4-5 网络表文件

(3)生成元器件列表

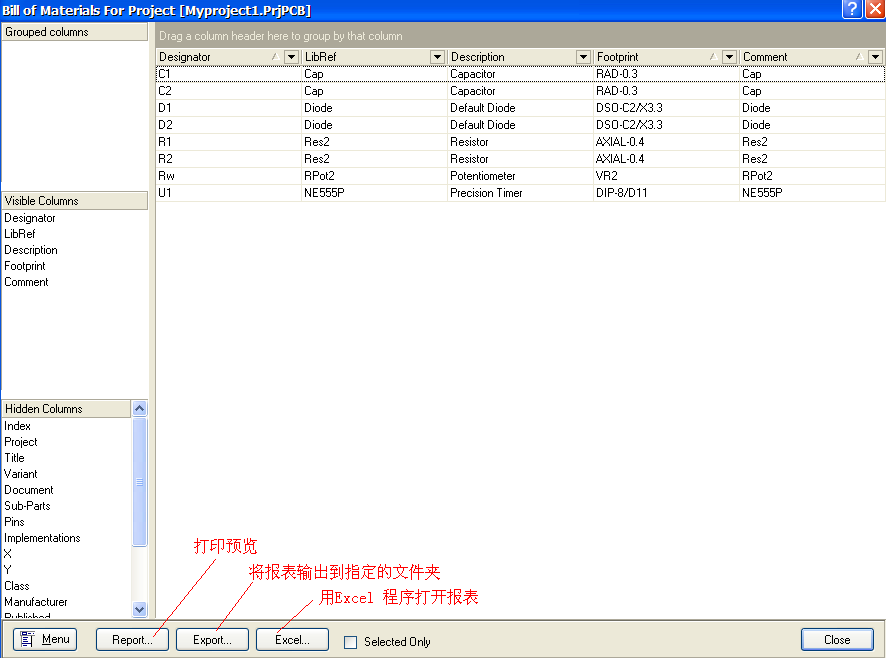

元器件列表主要用于整理电路原理图或一个项目中的所有元器件,主要包括元器件的名称、标注和封装等。

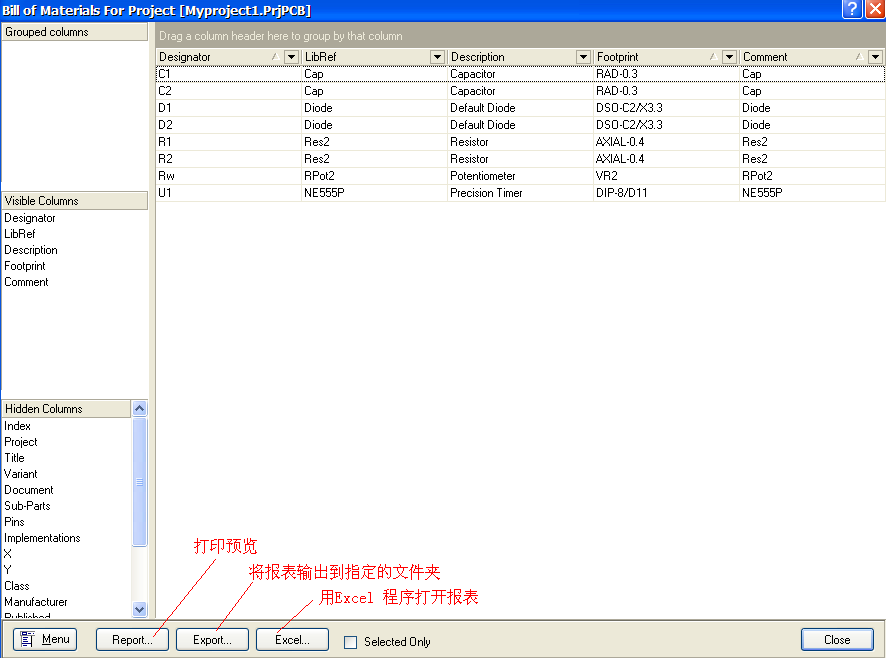

首先打开原理图文件,然后执行Report→Bill of Materials命令,系统将自动生成如图4-6所示的元器件列表。

图4-6元器件列表

单击Excel,可用Excel程序打开报表,如图4-7所示。

单击Export输出按钮,可将报表导出到指定的文件夹,报表的扩展名为.xls。如图4-8所示。

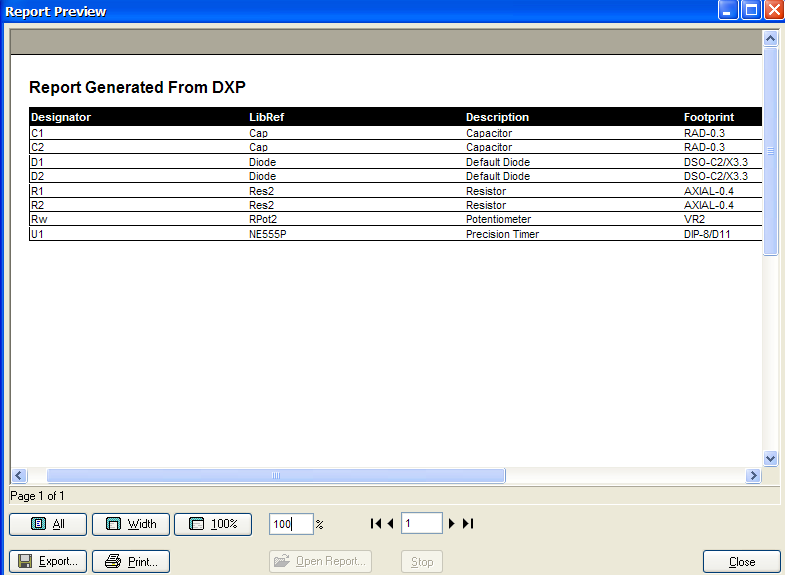

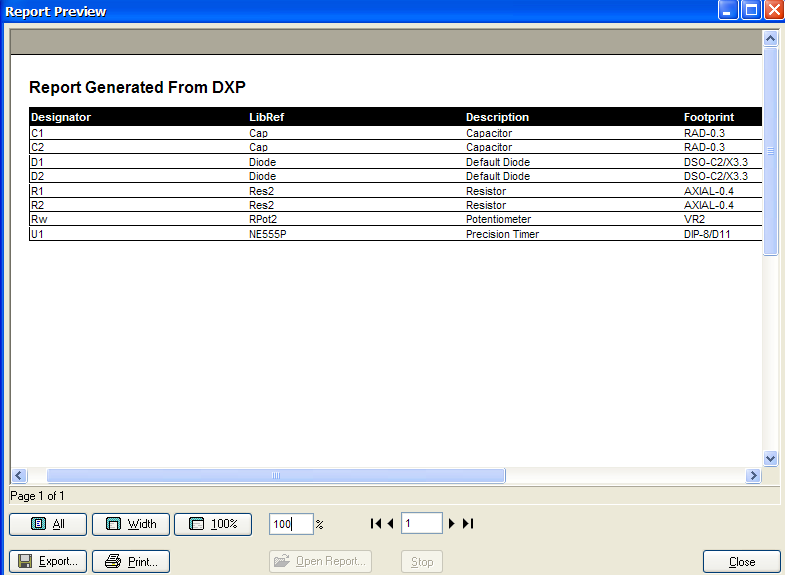

单击Report报告按钮,可以预览想要打印的报表。如图4-9所示。

图4-7 用Excel程序打开的元件报表

图4-8 报表存储路径选择对话框

图4-9 打印报表预览

输出文件清单(报表):ReportàExport保存清单,格式为.xls。

【练习】

参照范例要求对图2-21所示的单片机最小系统电路原理图进行编译,并生成网络表及元件报表。

学习编译项目,产生ERC报告,会纠正报告中的错误;会生成原理图的网络表、元器件列表。

【范例】

以图2-1所示的555定时器组成的振荡器电路原理图为例,生成该原理图的ERC表、网络表、元器件列表。

【步骤】

打开或新建一个工程文件Myproject1. PrjPCB,把振荡器电路原理图放入该工程下。

(1)产生ERC报告

ERC即电气规则检查。主要用于在进行PCB设计之前,对电路原理图中电路连接匹配的正确性进行检验。执行完该检查后,系统将自动在原理图中有错的地方加以标记,从而方便用户检查错误,提高设计质量和效率。

① 在对所绘原理图进行ERC检测之前应对ERC规则进行设置。ERC规则进行设置在“Options for Project”对话框实现,执行Project→Project Options命令,将弹出如图4-1所示的对话框。其中涉及到电路原理图检查的有Error Reporting(错误报告)和Connection Matrix(连接矩阵)两个。一般采用默认设置不需要对错误报告类型进行修改。

图4-1 项目管理选项对话框

② 编译项目 (ERC检查)

编译项目就是在设计文档中检查原理图的电气规则错误。执行菜单命令 Project / Compile PCB Project ,系统开始编译 Myproject1. PrjPCB 。当项目被编译时,在项目选项中设置的错误检查都会被启动,同时弹出 Message 窗口显示错误信息。如果原理图绘制正确,将不会弹出 Message 窗口。

故意把电阻R重名,编译后弹出如图4-2所示信息。

图4-2 ERC错误报告

双击一个出错信息前面的颜色方块,则会弹出与此错误有关的原理图信息,显示在Compile Error 对话框。如图4-3所示。

图4-3 Compile Error 对话框

从 Compile Error 对话框中单击错误跳转到原理图的违反对象进行检查或修改。此时修改对象高亮显示,电路图上的其他元件和导线模糊。修改完成后,可以单击图纸有下方的 Clear 按钮,清除图纸的模糊状态。

修改完成后,重新编译项目,直至不再显示错误为止。保存项目文件。

(2)生成网络表

网络表文件是简单的ASCII码文本文件,共包含两部分:元器件描述和元器件的网络连接描述。

执行主菜单命令 Design/Netlist/Protel,产生与原项目文件同名,后缀名为.net的网络表,这里生成的网络表名称即为Myproject1. net,如图4-4所示。

双击Myproject1. net 图标,将显示网表的详细内容。如图4-5所示。

图4-4 网络表的生成

图4-5 网络表文件

(3)生成元器件列表

元器件列表主要用于整理电路原理图或一个项目中的所有元器件,主要包括元器件的名称、标注和封装等。

首先打开原理图文件,然后执行Report→Bill of Materials命令,系统将自动生成如图4-6所示的元器件列表。

图4-6元器件列表

单击Excel,可用Excel程序打开报表,如图4-7所示。

单击Export输出按钮,可将报表导出到指定的文件夹,报表的扩展名为.xls。如图4-8所示。

单击Report报告按钮,可以预览想要打印的报表。如图4-9所示。

图4-7 用Excel程序打开的元件报表

图4-8 报表存储路径选择对话框

图4-9 打印报表预览

输出文件清单(报表):ReportàExport保存清单,格式为.xls。

【练习】

参照范例要求对图2-21所示的单片机最小系统电路原理图进行编译,并生成网络表及元件报表。